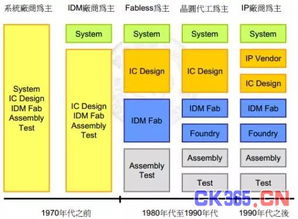

基于SoC与IP核复用技术实现综合业务接入系统的集成电路设计

随着通信技术的飞速发展,综合业务接入系统作为连接用户与核心网络的关键枢纽,其性能、集成度与成本效益日益成为业界关注的焦点。传统的多芯片分立解决方案已难以满足高带宽、多功能、低功耗及快速上市的需求。因此,采用片上系统(SoC)设计理念,结合成熟的IP核复用技术,成为实现下一代高性能、高集成度综合业务接入系统芯片的关键路径。

一、系统设计目标与架构规划

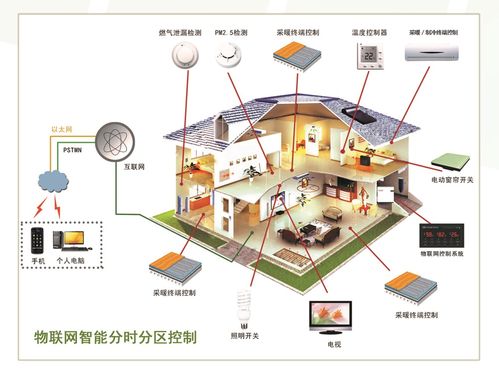

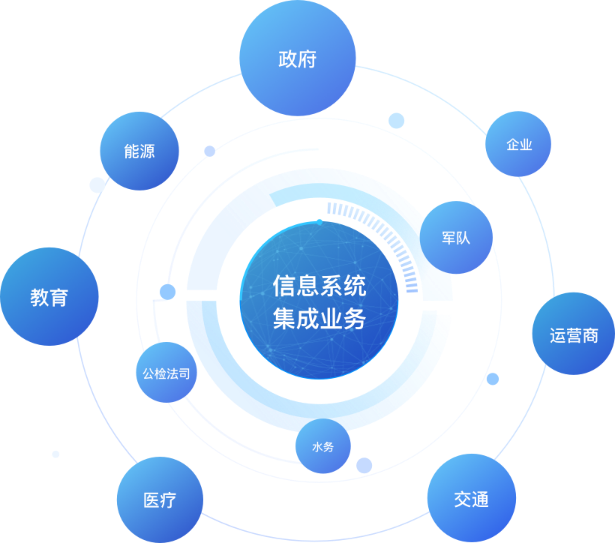

综合业务接入系统需要同时处理多种业务流,如传统的TDM语音、高速以太网数据、视频以及新兴的物联网接入等。基于SoC的设计目标,是构建一个高度集成的单芯片解决方案。其核心架构通常包括:

- 中央处理单元:采用高性能、低功耗的处理器核(如ARM Cortex-A/M系列),负责系统控制、协议处理和业务调度。

- 通信接口子系统:集成多种物理层(PHY)接口IP,如xDSL、GPON/EPON、GE/10GE以太网、E1/T1等,以支持多样化的接入媒介。

- 网络处理与交换单元:包含数据包处理引擎、流量管理器和高速交换矩阵IP,实现业务流的分类、整形、转发与汇聚。

- 存储子系统:集成DDR控制器、SRAM、Flash控制器等IP,为系统运行和数据缓冲提供支持。

- 外围与辅助单元:包括时钟管理、电源管理、DMA控制器、通用IO等通用IP模块。

采用IP核复用技术,可以快速地从已验证的IP库中选取上述模块,显著缩短设计周期,降低开发风险和成本。

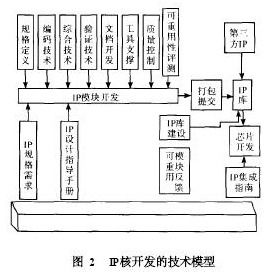

二、IP核的选择、集成与验证

IP核复用是SoC设计的基石。对于综合业务接入系统,关键的IP核包括:

- 处理器IP:选择经过市场广泛验证的处理器内核及配套的软件开发工具链。

- 通信接口IP:选择符合行业标准、性能达标的PHY和MAC层IP,确保与现有网络的兼容性。

- 互连总线IP:采用高性能、可扩展的片上互连标准(如AMBA AXI),作为IP模块间数据通信的“高速公路”。

集成过程并非简单的堆砌。设计团队需要:

- 进行精心的系统级建模与性能仿真,确保总线带宽、内存访问延迟等满足严苛的业务需求。

- 解决各IP核之间的时钟域、电压域隔离与同步问题。

- 设计统一的系统控制与状态寄存器映射,方便软件驱动开发。

- 实施全面的硬件/软件协同验证,在流片前确保系统功能的正确性。

三、物理设计与系统集成考量

当所有数字逻辑设计完成后,将进入物理实现阶段。此阶段面临的挑战包括:

- 规模与复杂度:高度集成的SoC可能包含数千万甚至上亿门电路,对布局布线工具和设计方法学提出极高要求。

- 功耗与热管理:集成众多功能模块,尤其是高速SerDes接口,功耗密度大。需要采用时钟门控、电源门控、动态电压频率调节等技术进行精细化管理,并在封装和散热上做相应考虑。

- 信号完整性:高速信号在芯片内部及封装内的传输需要严谨的仿真与设计,防止信号失真和串扰。

- 可测性设计:必须内置扫描链、内存BIST等DFT结构,以确保芯片制造后的高测试覆盖率和良率。

成功的系统集成,意味着从架构规划、IP集成、前端设计、后端物理实现到封装测试的全流程无缝衔接,最终交付一颗功能完备、性能达标、可靠稳定的芯片。

四、优势与展望

基于SoC和IP核复用技术设计综合业务接入芯片,带来了显著优势:

- 高集成度:将传统板级的多芯片系统浓缩于单一硅片,大幅减小设备体积和功耗。

- 高性能:片内高速互连和硬件加速单元,远超板级互连带宽,提升了系统处理能力。

- 低成本:大规模集成降低了整体物料成本和PCB设计复杂度;IP复用节省了大量重复开发投入。

- 灵活性高:可通过软件配置和可编程逻辑部分,适应不同应用场景和标准演进。

- 缩短上市时间:复用成熟可靠的IP核,使设计团队能聚焦于系统创新与差异化开发,加速产品面市。

随着5G固移融合、F5G全光接入及人工智能边缘计算的发展,综合业务接入系统芯片将朝着更高速率(如50G-PON、200G/400G以太网)、更高智能(内置AI处理单元)、更强安全(硬件级加密与信任根)的方向演进。SoC设计与IP复用技术,将继续作为支撑这一演进的核心引擎,驱动接入网络向更高效、更智能、更开放的方向持续发展。

如若转载,请注明出处:http://www.shhuill.com/product/49.html

更新时间:2026-01-12 02:11:28